# EDA技术及其应用

# 第2章 Quartus II 设计向导

### 2.1 原理图输入设计方法的特点

- ◇进行几乎任意层次的数字系统设计。

- ◇对系统中的任一层次,或任一元件的功能进行精确的时序 仿真,精度达**0.1ns**。

- ◇通过时序仿真,迅速定位电路系统的错误,并随时纠正。

- ◇对设计方案进行随时更改,并储存设计过程中所有的电路 和测试文件入档。

- ◇通过编译和下载,在FPGA上对设计项目随时进行硬件测试验证。

- ◇如果使用FPGA和配置编程方式,将不会有器件损坏和损耗的问题。

- ◇符合现代电子设计技术规范。

#### **Quartus II**

- 2.2.1 建立工作库文件夹和编辑设计文件

- (1)新建一个文件夹。

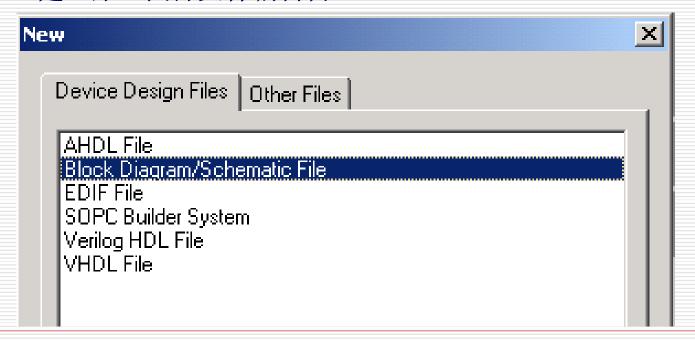

- (2)建立原理图源文件编辑窗。

图2-1 选择编辑文件类型

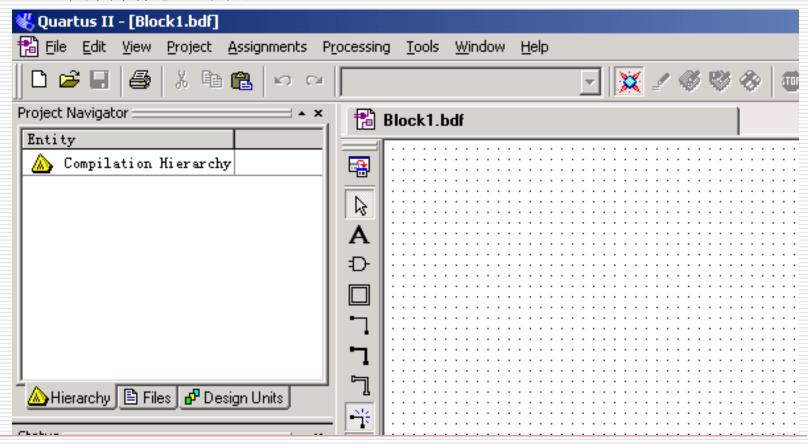

(3)编辑构建电路图。

图2-2 打开原理图编辑窗

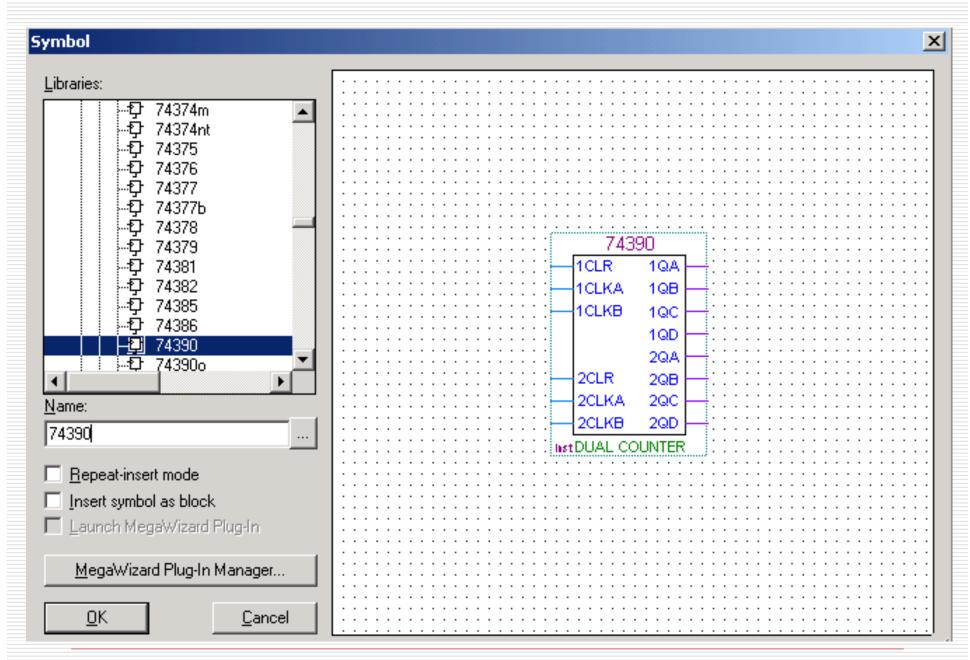

图2-3 调入需要的宏功能元件(Symbol)

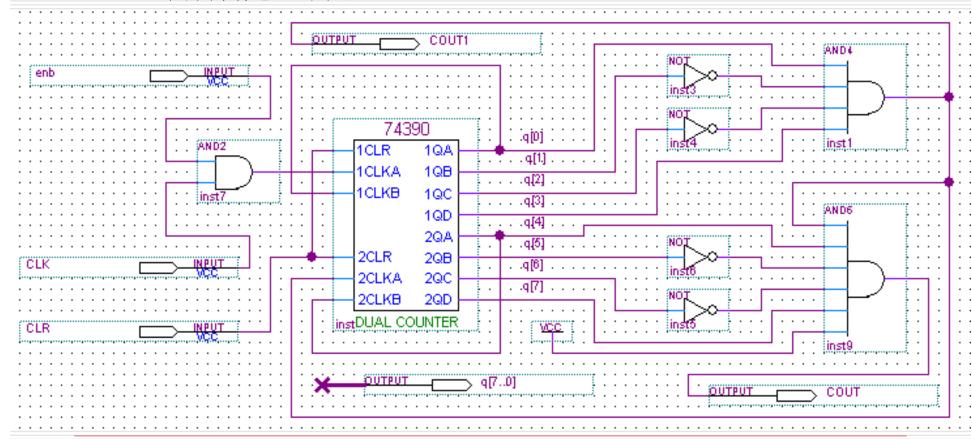

(3)编辑构建电路图。

图2-4 两位十进制计数器电路图

#### (4) 文件存盘。

选择File→Save As命令,找到已设立的文件夹路径为d:\ MY\_PROJECT,存盘文件名为cnt10.bdf。若出现问句"Do you want to create…"时,若单击"是"按钮,则直接进入创建工程流程。若单击"否"按钮,可按以下的方法进入创建工程流程。

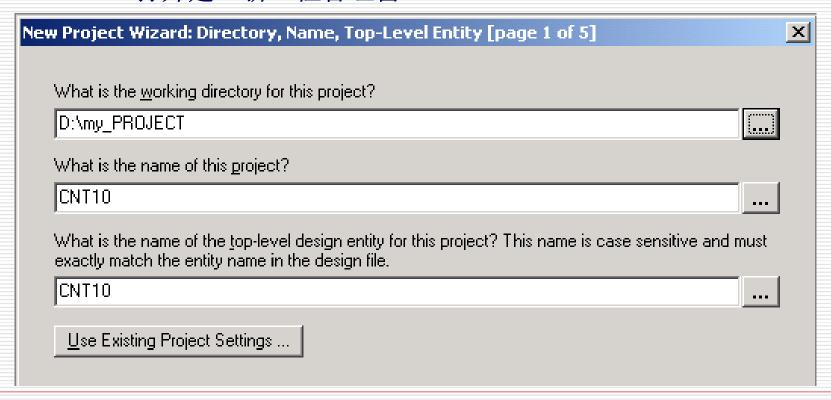

#### 2.2.2 创建工程

(1) 打开建立新工程管理窗。

图2-5 利用"New Preject Wizard"创建工程cnt10

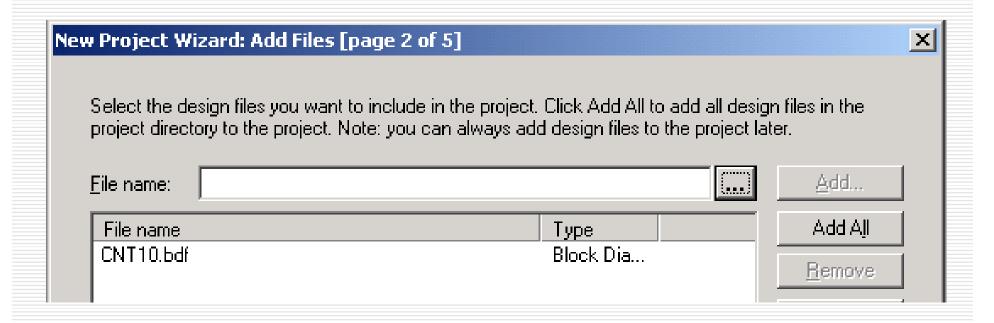

(2)将设计文件加入工程中。

图2-6 将所有相关的文件都加入进此工程

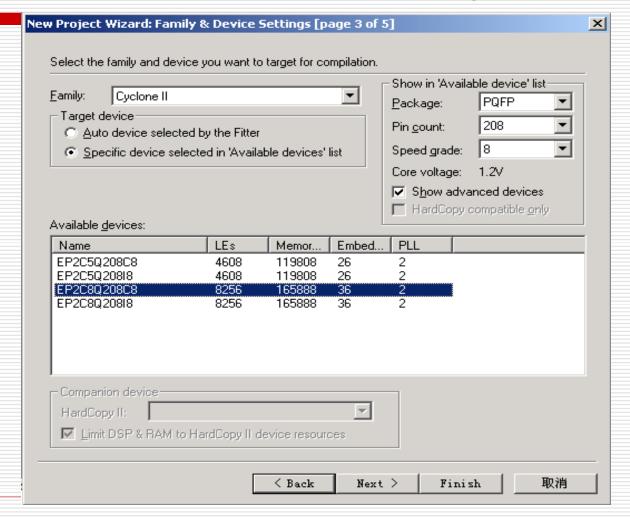

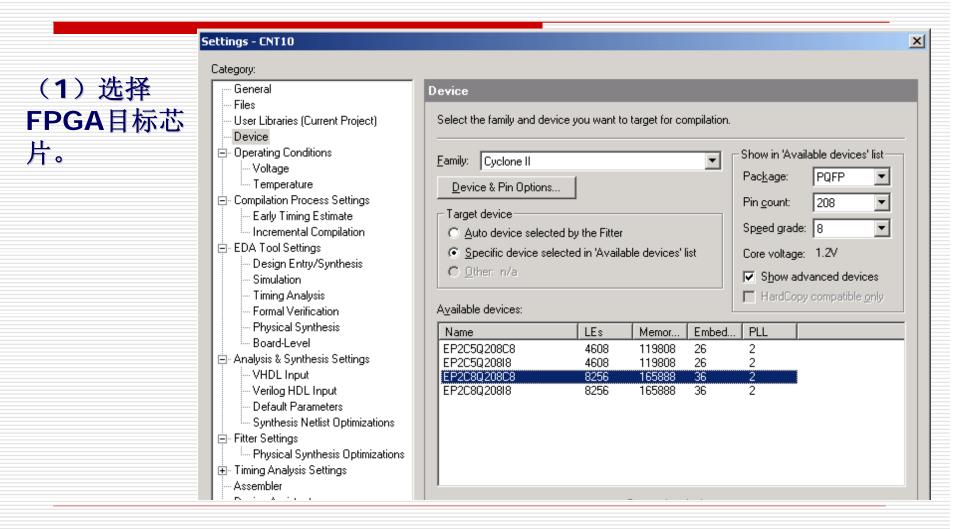

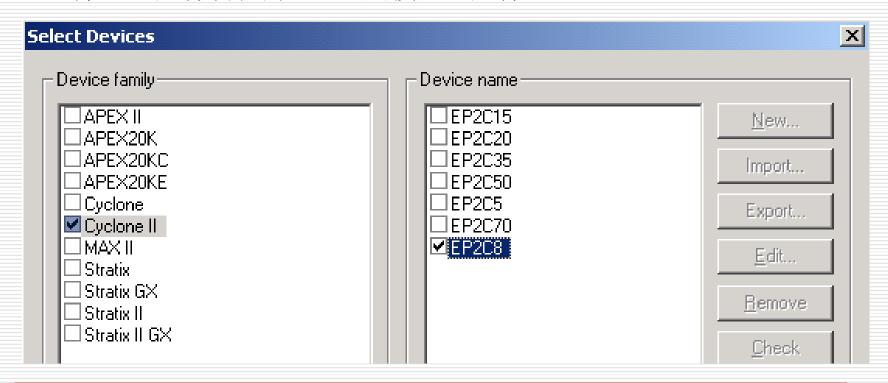

(3)选择目标芯片。

图2-7 选择目标器件EP2C8Q208C8

- (4) 工具设置。

- (5)结束设置。

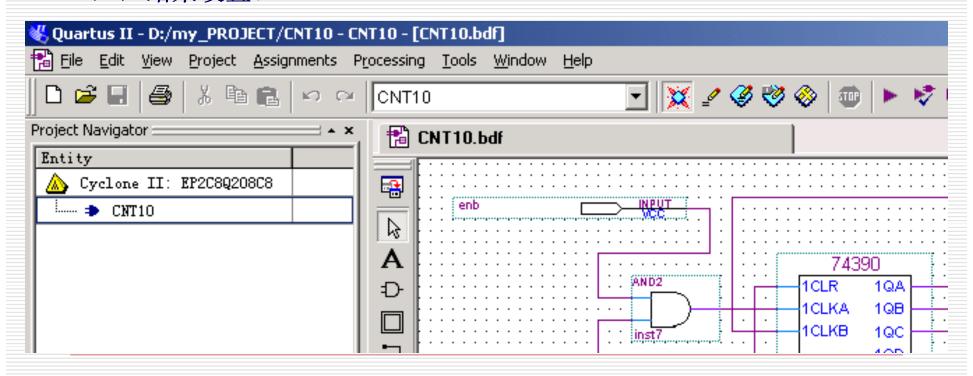

图2-8 CNT10工程管理窗

#### 2.2.3 功能分析

图2-9 74390的真值表

Dual Decade Counter

Default Signal Levels: GND-1CLR, 1CLKB, 2CLR, 2CLKB

VCC-1CLKA, 2CLKA

#### AHDL Function Prototype (port name and order also apply to Verilog HDL):

FUNCTION 74390 (1clr, 1clka, 1clkb, 2clr, 2clka, 2clkb) RETURNS (1qd, 1qc, 1qb, 1qa, 2qd, 2qc, 2qb, 2qa);

| Inputs |     | 1 |    | Outp | outs |    |

|--------|-----|---|----|------|------|----|

| CLR    | CLK | - | QD | QC   | QB   | QA |

| Н      | Х   | ı | L  | L    | L    | L  |

| H<br>L | l   | i |    | Соц  |      |    |

#### Possible Counting Configurations:

Bi-Quinary: QD Connected to CLKA Decade: QA Connected to CLKB QC Count QD QB Count QD QB 0 2 3 4 5 6 8 9

#### 2.2.4 编译前设置

图2-10 选择目标器件EP2C8Q208C8

### 2.2.4 编译前设置

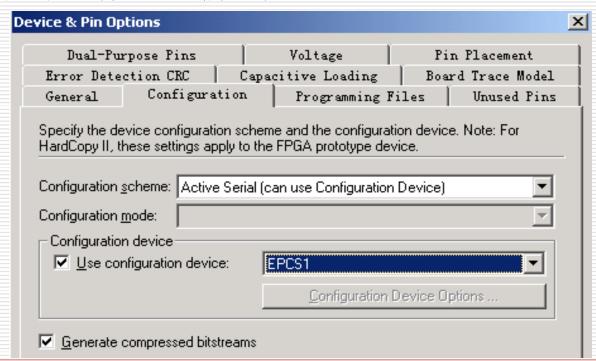

(2) 选择配置器件的工作方式。

| Dual-Pu                                                                    | rpose Pins                                                                                                |                            | Voltage               | Pi:      | n Placement       |

|----------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------|----------------------------|-----------------------|----------|-------------------|

| Error Dete                                                                 | ction CRC                                                                                                 | Capa                       | citive Loading        | Boar     | rd Trace Model    |

| General                                                                    | Configurat                                                                                                | ion                        | Programming Fi        | les      | Unused Pins       |

| scheme.<br>Options:                                                        |                                                                                                           |                            | options are not deper | ident on | the configuration |

| . I Auto rootor                                                            |                                                                                                           |                            |                       |          |                   |

| ✓ Auto-restart configuration after error  Release clears before tri-states |                                                                                                           |                            |                       |          |                   |

| □Release cl                                                                | ears before tri-stal                                                                                      | tes                        | (CLVIICD)             |          |                   |

| □Release cl<br>□Enable use                                                 | ears before tri-stal<br>er-supplied start-up                                                              | tes<br>piclocki            |                       | •••••    |                   |

| □Release cl<br>□Enable use<br>□Enable de                                   | ears before tri-stal<br>er-supplied start-up<br>vice-wide reset (D                                        | tes<br>piclock (<br>EV_CLF | Rn)                   |          |                   |

| □Release cl<br>□Enable use<br>□Enable dev<br>□Enable dev                   | ears before tri-stal<br>er-supplied start-up                                                              | tes<br>piclock (<br>EV_CLF | Rn)                   |          |                   |

| □Release cl<br>□Enable use<br>□Enable dev<br>□Enable dev                   | ears before tri-stal<br>er-supplied start-up<br>vice-wide reset (D<br>vice-wide output e<br>T_DONE output | tes<br>piclock (<br>EV_CLF | Rn)                   |          |                   |

图2-11选择配置器件的工作方式

#### 2.2.4 编译前设置

(3) 选择配置器件和编程方式。

| Dual-Pur                                  | pose Pins     | Voltage                          | Pin     | Placement     |

|-------------------------------------------|---------------|----------------------------------|---------|---------------|

| Error Detec                               |               | acitive Loading                  | Board   | l Trace Model |

| General                                   | Configuration | Programming Fi                   | les     | Unused Pins   |

|                                           |               |                                  |         |               |

| Configuration <u>n</u>                    | - ·           | can use Configuration I          | Device) | <b>*</b>      |

| Configuration <u>n</u><br>— Configuration | node:         | can use Configuration  <br>EPCS1 | Device) |               |

图2-12 选择配置器件型号和压缩方式

#### 2.2.4 编译前设置

- (4)选择输出设置。

- (5) 选择目标器件闲置引脚的状态。

图2-12 选择配置器件型号和压缩方式

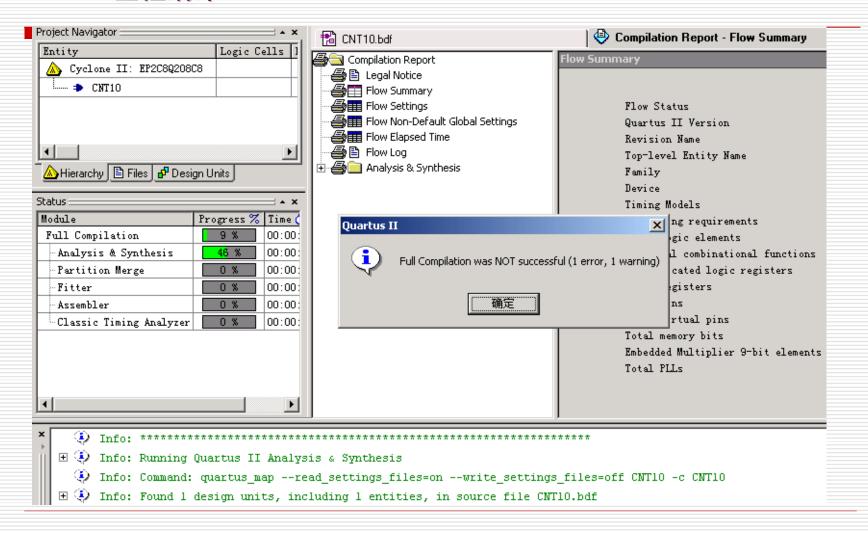

#### 2.2.5 全程编译

图2-13 全程编译后出现报错信息

#### 2.2.6 功能测试

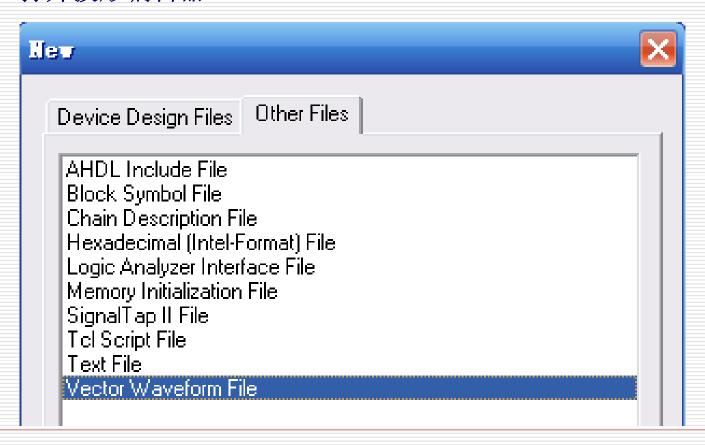

(1) 打开波形编辑器。

图2-14 选择编辑矢量波形文件

#### 2.2.6 功能测试

### (1) 打开波形编辑器。

图2-15 波形编辑器

2.2.6 功能测试

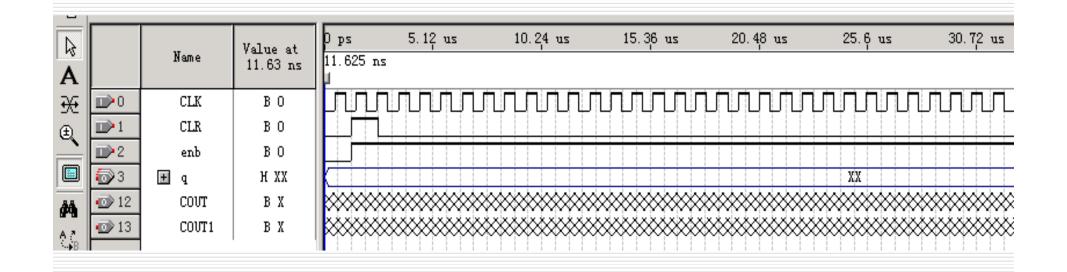

(2)设置仿真时间区域。

### 2.2.6 功能测试

(3)波形文件存盘。

| my_PROJECT         |                 | v            | ← 🗈 💣 🖩 |       |

|--------------------|-----------------|--------------|---------|-------|

| <u>□</u> db        |                 |              |         |       |

|                    |                 |              |         |       |

|                    |                 |              |         |       |

|                    |                 |              |         |       |

|                    |                 |              |         |       |

| )<br>文件名(M):       | ENTILO          |              | ▼       | 保存(S) |

| 保存类型 ( <u>T</u> ): | Vector Waveform | File (*.vwf) | •       | 取消    |

图2-17 vwf激励波形文件存盘

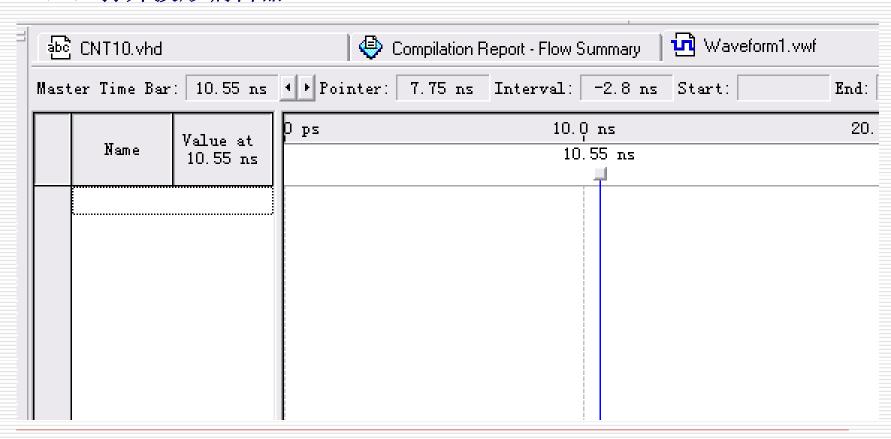

2.2.6 功能测试

(4) 将工程cnt10的端口信号名选入波形编辑器中。

图2-18 向波形编辑器拖入信号节点

2.2.6 功能测试

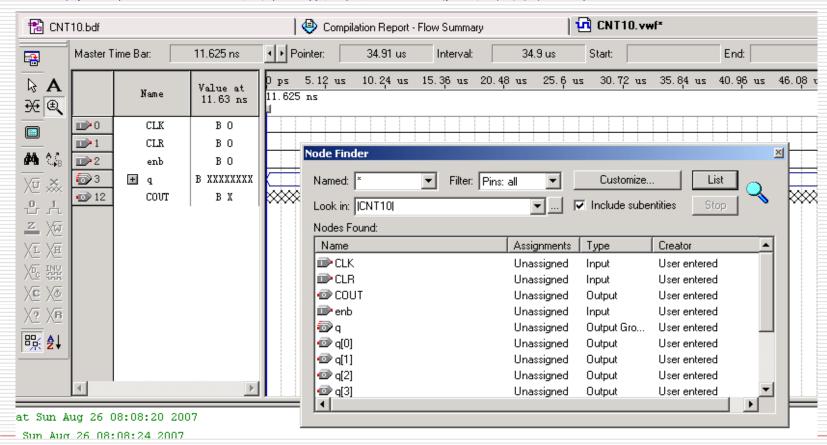

(5) 编辑输入波形(输入激励信号)。

图2-19 准备给CLK设置时钟

图2-20 为CLK设置周期

### 2.2.6 功能测试

(6) 总线数据格式设置。

| Node Properties                         |             |  |  |  |  |

|-----------------------------------------|-------------|--|--|--|--|

| General                                 |             |  |  |  |  |

| <u>N</u> ame:                           |             |  |  |  |  |

| <u>T</u> ype:                           | OUTPUT 🔻    |  |  |  |  |

| Value type:                             | 9-Level     |  |  |  |  |

| <u>R</u> adix:                          | Hexadecimal |  |  |  |  |

| Bus <u>w</u> idth:                      | 8 =         |  |  |  |  |

| Display gray code count as binary count |             |  |  |  |  |

2.2.6 功能测试

(6) 总线数据格式设置。

#### 2.2.6 功能测试

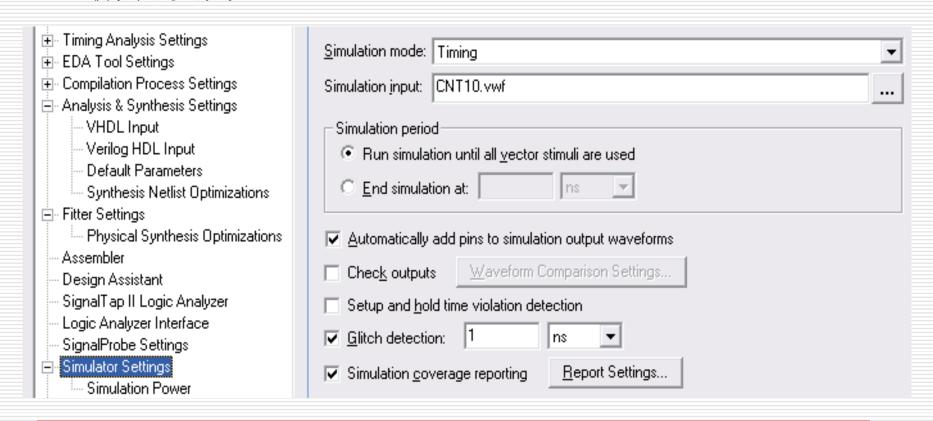

#### (7) 仿真器参数设置。

2.2.6 功能测试

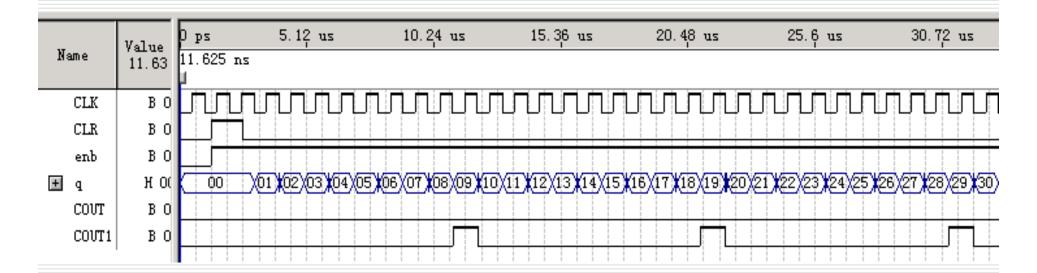

- (8) 启动仿真器。

- (9)观察仿真结果。

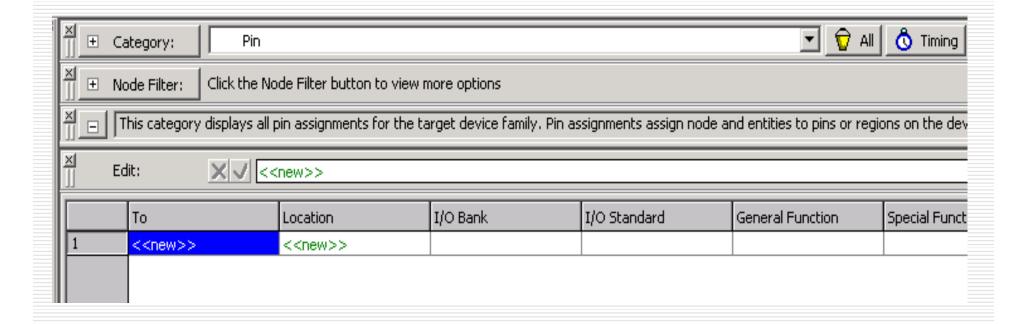

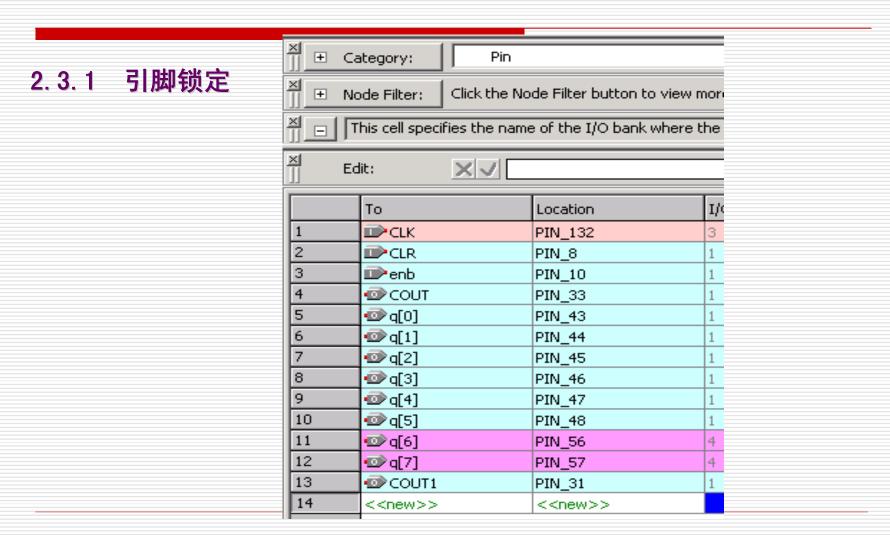

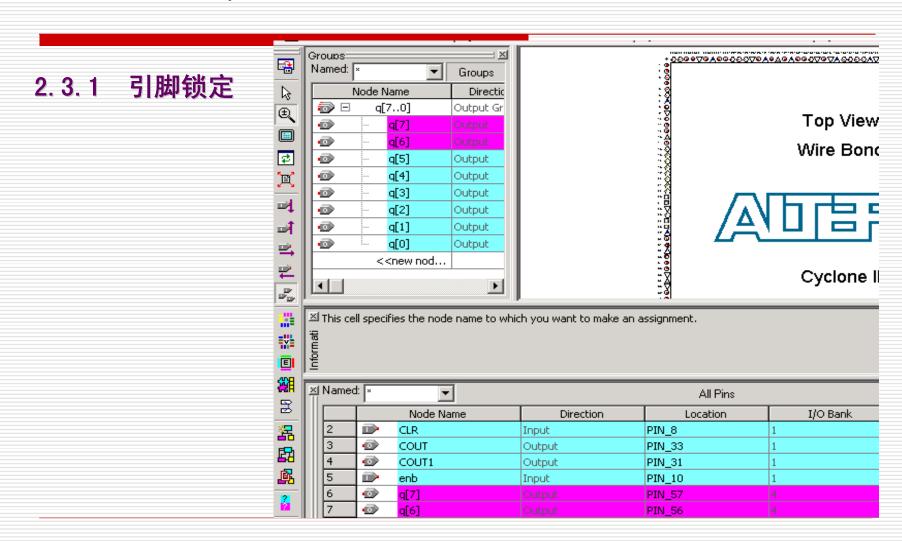

#### 2.3.1 引脚锁定

图2-26 表格式引脚锁定对话框

图2-27 图形式引脚锁定对话框

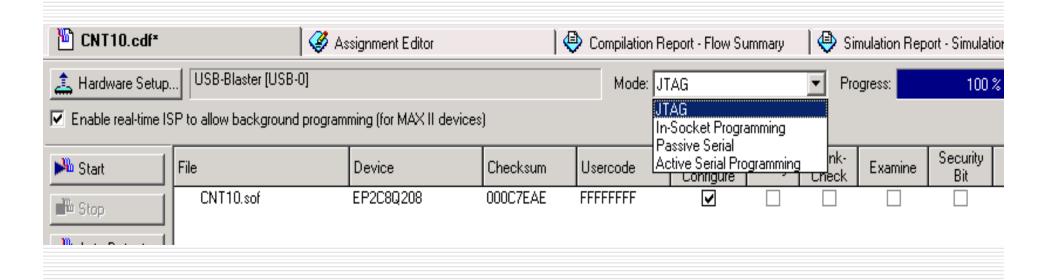

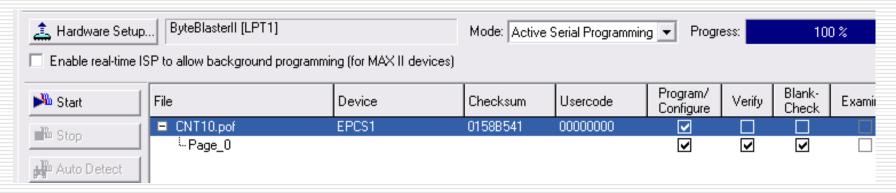

#### 2.3.2 配置文件下载

(1) 打开编程窗和配置文件。

#### 2.3.2 配置文件下载

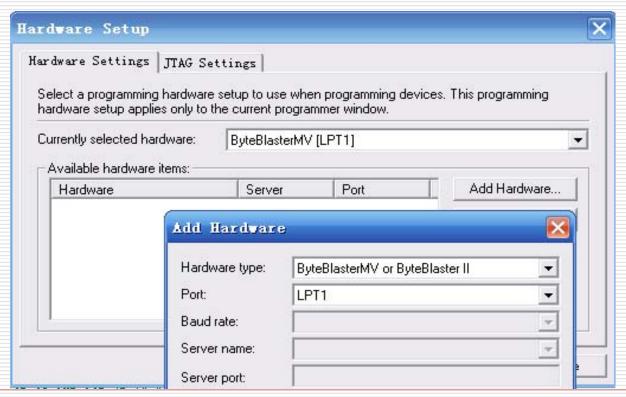

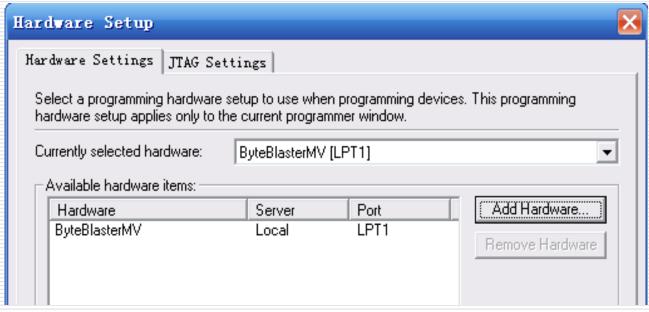

(2)设置编程器。

图2-29加入编程下载方式

#### 2.3.2 配置文件下载

(2)设置编程器。

图2-30 双击选中的编程方式名

(3) 硬件测试。

#### 2.3.3 AS模式直接编程配置器件

1. 选择编程模式和编程目标文件

图2-31 ByteBlaster II接口AS模式编程窗口

- 2. 选择接插模式

- 3. AS模式编程下载

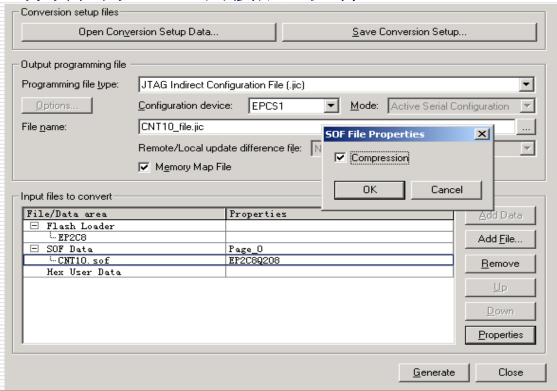

- 2.3.4 JTAG间接模式编程配置器件

- 1. 将SOF文件转化为JTAG间接配置文件

- 2.3.4 JTAG间接模式编程配置器件

- 1. 将SOF文件转化为JTAG间接配置文件

图2-33 选定SOF文件后,选择文件压缩

## 2.3 引脚设置和下载

- 2.3.4 JTAG间接模式编程配置器件

- 2. 下载JTAG间接配置文件

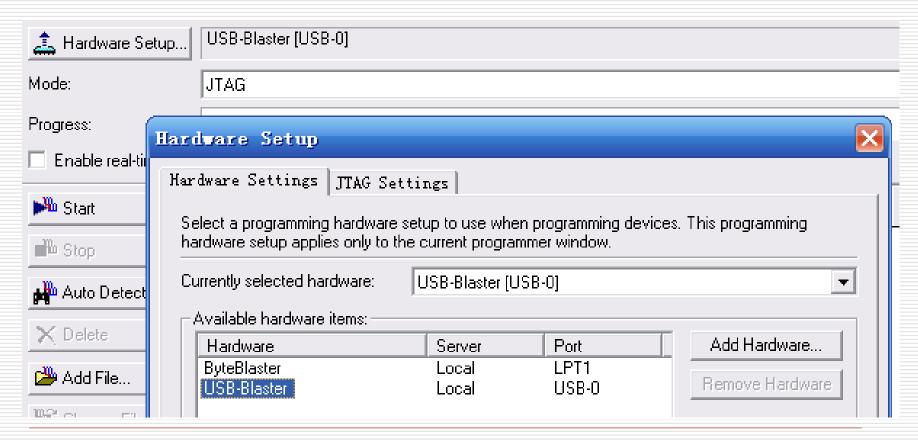

| Aardware Setup USB-Blaster [USB-0]                                          |                             |        |          | Mode: JTAG |                       |        | ▼ Prog          |  |  |

|-----------------------------------------------------------------------------|-----------------------------|--------|----------|------------|-----------------------|--------|-----------------|--|--|

| ▼ Enable real-time ISP to allow background programming (for MAX II devices) |                             |        |          |            |                       |        |                 |  |  |

| <b>№</b> Start                                                              | File                        | Device | Checksum | Usercode   | Program/<br>Configure | Verify | Blank-<br>Check |  |  |

| <b>™</b> Stop                                                               | □ Factory default SFL image | EP2C8  | 00F6C1AB | FFFFFFF    | <b>▼</b>              |        |                 |  |  |

|                                                                             | cnt10_file.jic              | EPCS1  | 000DA976 |            | V                     | V      |                 |  |  |

| <b>₩</b> Auto Detect                                                        |                             |        |          |            |                       |        |                 |  |  |

## 2.3 引脚设置和下载

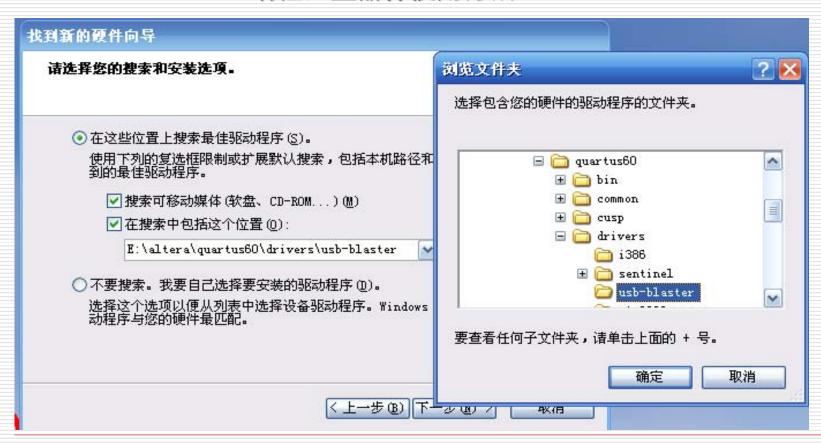

#### 2.3.5 USB Blaster编程配置器件使用方法

图2-35 安装USB驱动程序

# 2.3 引脚设置和下载

#### 2.3.5 USB Blaster编程配置器件使用方法

图2-36 设置JTAG硬件功能

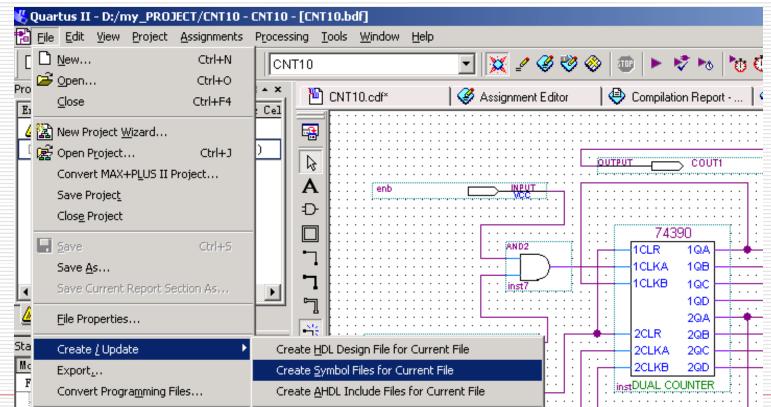

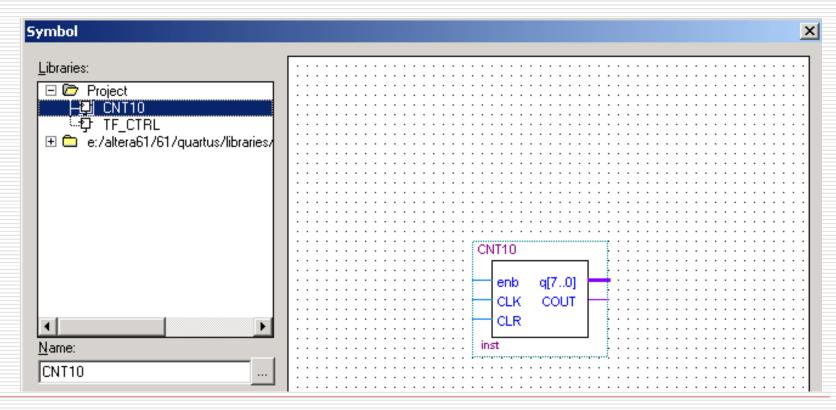

- 2.4.1 8位十进制计数器的设计

- 1. 构建元件符号

图2-37 将原理图设计生成一个底层的单独元件(Symbol)

- 2.4.1 8位十进制计数器的设计

- 2. 构建顶层文件

图2-38 从当前工程路径中调入元件CNT10

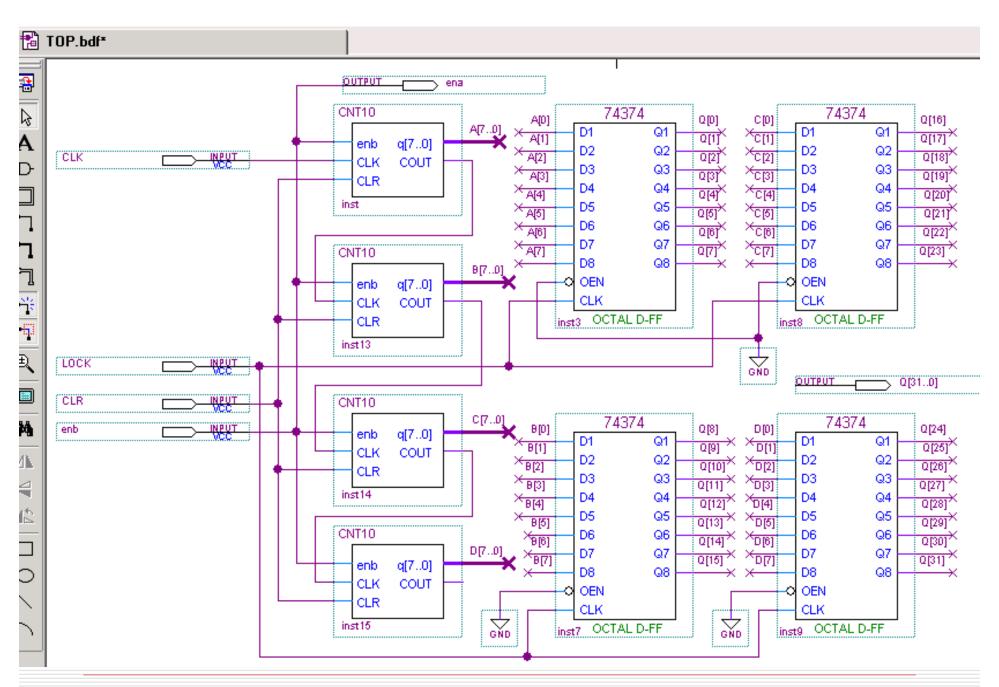

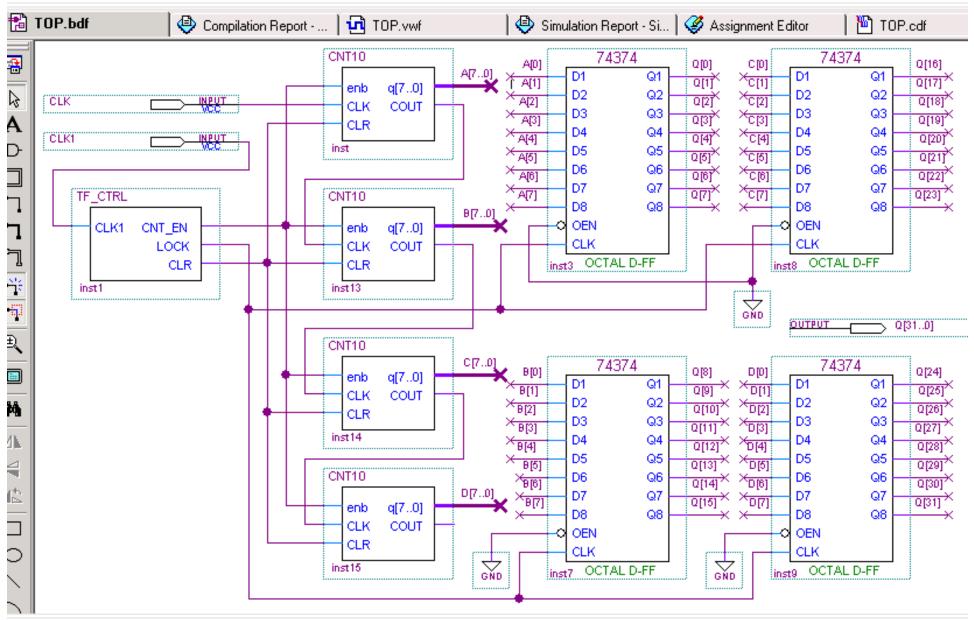

图2-39 两位十进制频率计顶层设计原理图文件

### 3. 功能分析

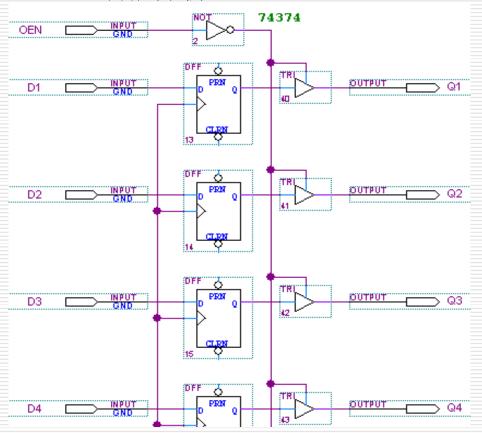

图2-39 两位十进制频率计顶层设计原理图文件

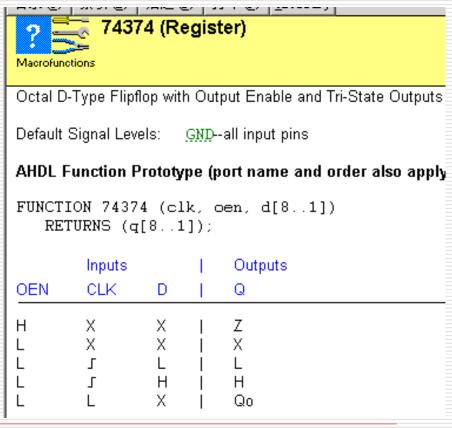

图2-41 74374真值表

- 2.4.1 8位十进制计数器的设计

- 4. 全程编译

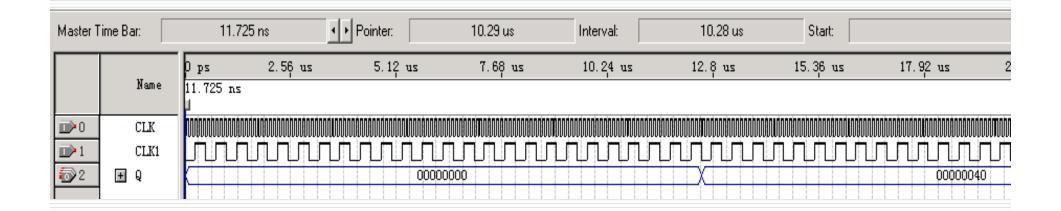

- 5. 时序仿真

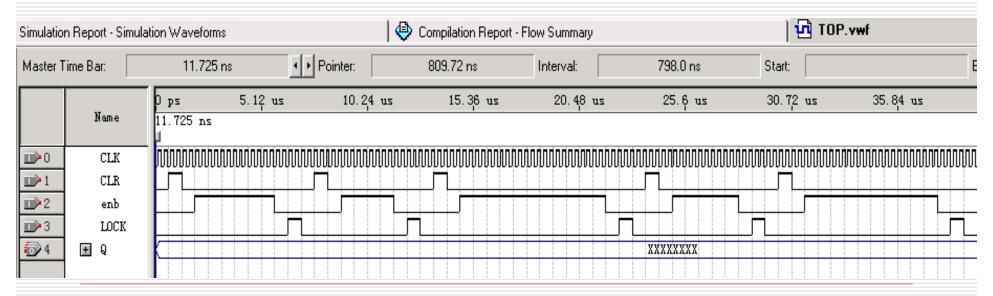

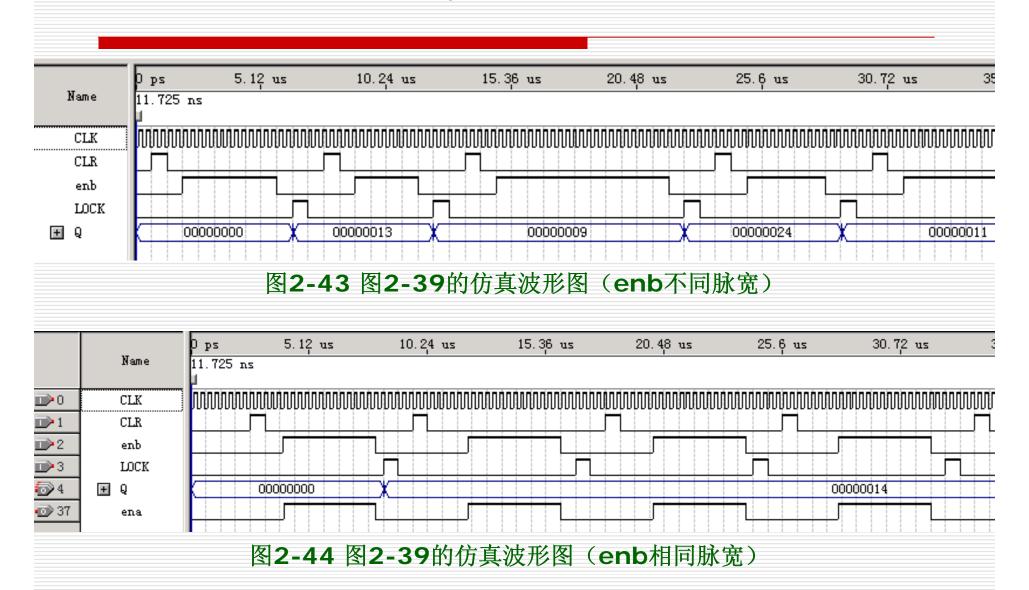

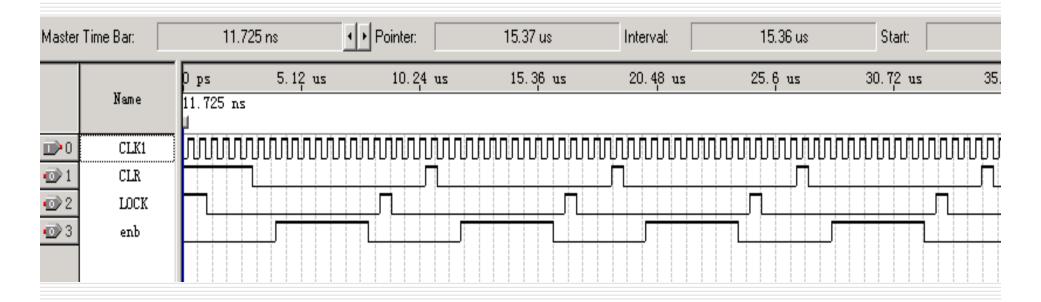

图2-42 图2-39的仿真激励波形图,或称矢量波形文件

#### 2.4.2 硬件测试与实验

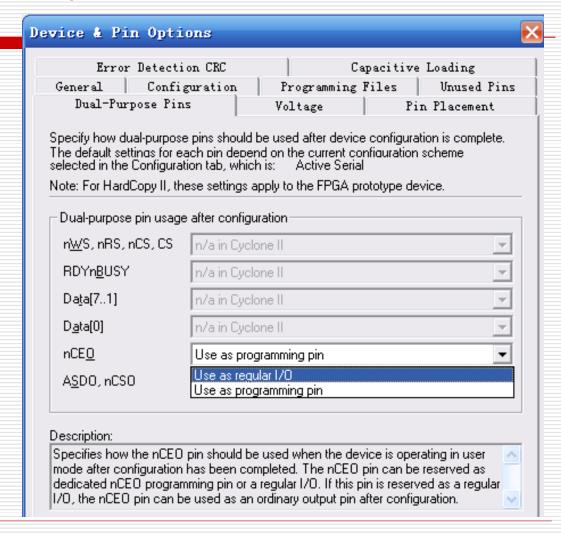

图2-45 将引脚nCEO设定为I/O口

## 2.5 8位十进制频率计设计

#### 2.5.1 时序控制器设计

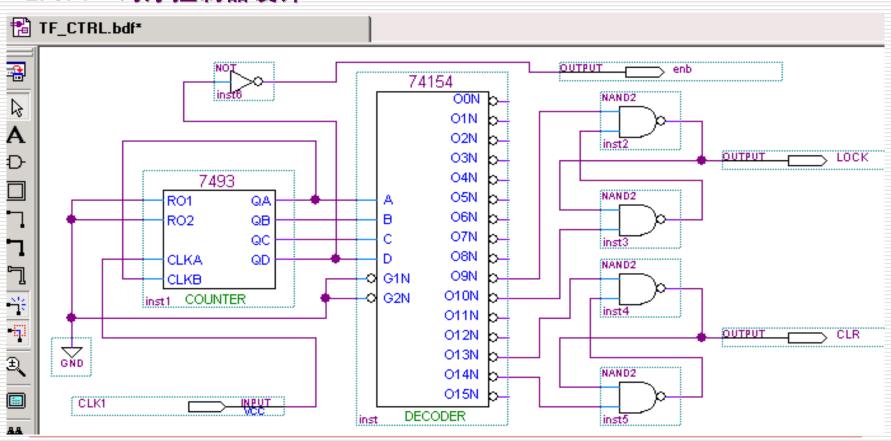

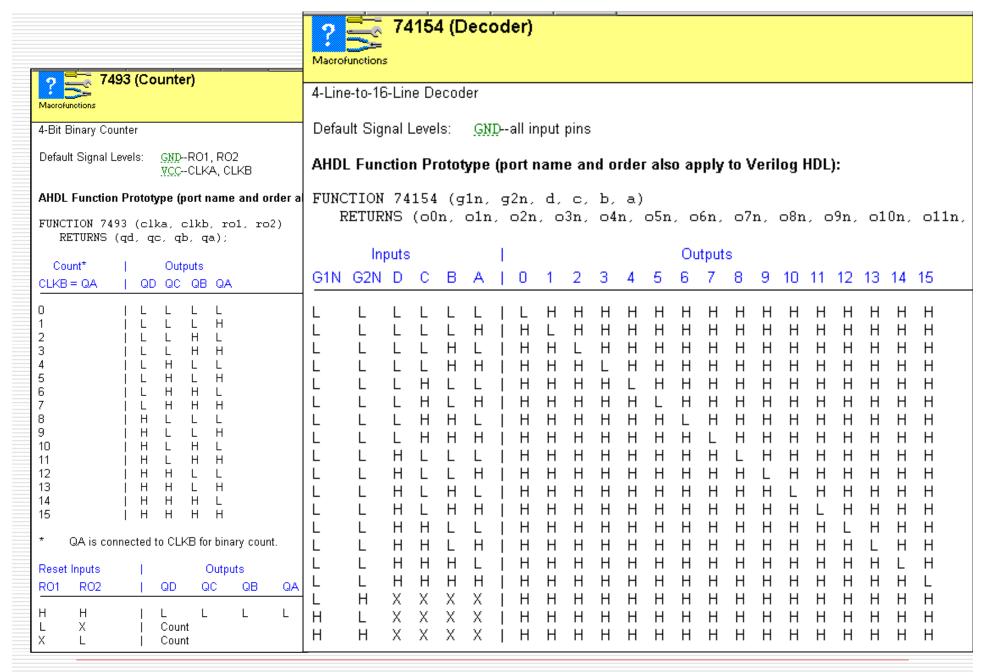

图2-46 频率计测频时序控制器电路

## 2.5 8位十进制频率计设计

#### 2.5.1 时序控制器设计

#### 2.5.2 顶层电路设计与测试

图2-50 测频时序控制电路图5-54 频率计顶层电路原理图

## 2.5 8位十进制频率计设计

#### 2.5.2 顶层电路设计与测试

### 习 题

- 2-1. 归纳利用Quartus II 进行原理图输入设计的流程。

- 2-2. 参考Quartus II的Help,详细说明Assignments菜单中Settings对话框的功能。

- (1) 说明其中的Timing Requirements & Options的功能、使用方法和检测途径。

- (2) 说明其中的Compilation Process的功能和使用方法。

- (3) 说明Analysis & Synthesis Setting的功能和使用方法,以及其中的Synthesis Netlist Optimization的功能和使用方法。

- (4) 说明Fitter Settings中的Design Assistant和Simulator功能,举例说明它们的使用方法。

- 2-3. 概述Assignments菜单中Assignment Editor的功能,举例说明。

- 2-4. 传统数字电路实验中,常用插导线的方法连接元件电路。根据已掌握的知识试说明,此种设计方法对系统的正常运行有何不利,为什么?

### 习 题

- 2-5. 时序仿真和功能仿真有何异同点?

- 2-6. 建立时序仿真中VWF文件的激励波形有何需要注意之处?

- **2-7**. 为什么要FPGA配置器件?对专用配置器件EPCS1,有几种编程方法?如何进行?

- 2-8. 如何构建一个多层次设计工程?

- 2-9. 在什么情况下必须对设计锁定引脚?锁定引脚有几种方法?如何完成?

- 2-10. 详细说明图2-43中各信号波形的功能,并说明,如果没有CLR信号,enb第4个高电平脉冲后,Q等于几?。说明图2-50所示的频率计中的CLR控制信号有何作用。

- 2-11. 提出两个新方案,取代图2-46电路的功能(注,输出波形不一定与图

- 2-49相同,但必须能用于图2-50的频率计的正确控制)

- 2-12. 提出一个新方案,取代图2-4的功能。

- **2-13**. 基于Quartus II 设计平台,用**74148**和与非门实现**8421BCD**优先编码器(止于时序仿真)。

### 习 题

- **2-14**. 基于Quartus II 设计平台,用3片74139组成一个5-24线译码器(止于时序仿真)。

- 2-15. 基于Quartus II 设计平台,用74283加法器和逻辑门设计实现一位8421BCD码加法器电路,输入输出均是BCD码,CI为低位的进位信号,CO为高位的进位信号,输入为两个1位十进制数A,输出用S表示(止于时序仿真)。

- **2-16**. 基于Quartus II 设计平台,设计一个**7**人表决电路,参加表决者**7**人,同意为**1**,不同意为**0**,同意者过半则表决通过,绿指示灯亮;表决不通过则红指示灯亮(止于时序仿真)。

- **2-17**. 基于Quartus II 设计平台,自选prim和mf库中的元件设计一个周期性产生二进制序列**01001011001**的序列发生器,用移位寄存器或用同步时序电路实现,并用时序仿真器验证其功能。

- 2-18. 基于Quartus II 设计平台,用D触发器构成按循环码(000->001->011->111->101->100->000)规律工作的六进制同步计数器(止于时序仿真)。

- **2-19**. 基于Quartus II 设计平台,应用4位全加器和74374构成4位二进制加法计数器(止于时序仿真)。

### 习题

- **2-20**. 基于Quartus II 设计平台,用**74194**、**74273**、D触发器等器件组成**8**位串入并出的转换电路,要求在转换过程中数据不变,只有当**8**位一组数据全部转换结束后,输出才变化一次(止于时序仿真)。

- 如果使用74299、74373、D触发器和非门来完成上述功能,应该有怎样的电路?

- 2-21. 基于Quartus II 设计平台,用一片74163和两片74138构成一个具有12路脉冲输出的数据分配器。要求在原理图上标明第1路到第12路输出的位置。若改用一片74195代替以上的74163,试完成同样的设计(止于时序仿真)。

- 2-22. 基于Quartus II 设计平台,用同步时序电路对串行二进制输入进行奇偶校验,每检测5位输入,输出一个结果。当5位输入中1的数目为奇数时,在最后一位的时刻输出1。

- **2-23**. 基于Quartus II 设计平台,用**7490**设计模为**872**的计数器,且输出的个位、十位、百位都应符合**8421**码权重。

- **2-24**. 基于Quartus II 设计平台,用**74161**设计一个**97**分频电路,用置**O**和置数两种方法实现。

- **2-25**. 基于Quartus II 设计平台,某通信接收机的同步信号为巴克码**1110010**。设计一个检测器,其输入为串行码**x**,输出为检测结果**y**,当检测到巴克码时,输出**1**。

- 2-1 8位十进制频率计设计

- 2-2 用原理图输入法设计8位全加器

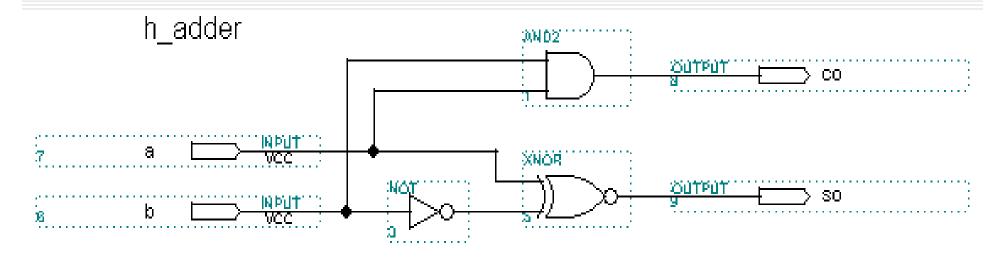

表2-1 半加器h\_adder逻辑功能真值表

| a | b | SO | со |

|---|---|----|----|

| 0 | 0 | 0  | 0  |

| 0 | 1 | 1  | 0  |

| 1 | 0 | 1  | 0  |

| 1 | 1 | 0  | 1  |

### 2-2 用原理图输入法设计8位全加器

图2-52 半加器h\_adder电路图

### 2-2 用原理图输入法设计8位全加器

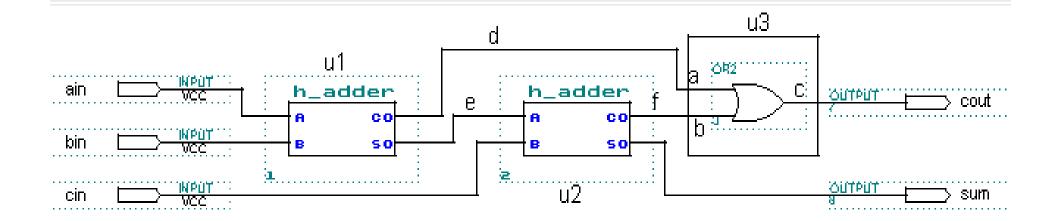

图2-53 全加器f\_adder电路图

#### 2-3 计时系统设计

- (1) 仿照本章给出的完整设计流程设计一个时钟,能计时、分、秒。时、分、秒分别用两位数码管显示。能用键校准时、分、秒。完成实验报告。

- (2) 设计一个定时器。能定时、分; 能用键设定时和分。完成实验报告。

- (3) 设计一个秒表。能显示分、秒。分的最大值是59分; 秒的最大值是59秒点

- **99**。即计秒精度是百分之一秒。用键能控制秒表的清**0**、开始计时和停止计时。 完成实验报告。

#### 2-4 数字系统设计

分别给出以上习题中的2-15、2-16、2-20、2-21、2-22的完整设计流程,包括系统构建、系统设计、时序仿真、引脚锁定、FPGA硬件测试和EPCS配置器件编程。分别完成实验报告。